Board:asus/m4a785t-m

The wiki is being retired!

Documentation is now handled by the same processes we use for code: Add something to the Documentation/ directory in the coreboot repo, and it will be rendered to https://doc.coreboot.org/. Contributions welcome!

Status

| Device/functionality | Status | Comments | ||||||

|---|---|---|---|---|---|---|---|---|

| CPU | ||||||||

| CPU works | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Tested: AMD Athlon64 X2 250. | ||||||

| L1 cache enabled | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | Not tested yet | ||||||

| L2 cache enabled | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | Not tested yet | ||||||

| L3 cache enabled | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Multiple CPU support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Multi-core support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| Hardware virtualization | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | KVM seem to work | ||||||

| RAM | ||||||||

| EDO | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| SDRAM | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| SO-DIMM | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| DDR | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | N/A | ||||||

| DDR2 | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| DDR3 | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | 2G works, 4G(2 * 2G) works with lastest coreboot | ||||||

| Dual channel support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| ECC support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| On-board Hardware | ||||||||

| On-board IDE 3.5" | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Tested: 500GB HDD | ||||||

| On-board IDE 2.5" | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board SATA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Tested some ports, works fine | ||||||

| On-board SCSI | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board USB | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | USB keyboard works | ||||||

| On-board VGA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Tested:analog VGA and HDMI,dual screen. | ||||||

| On-board Ethernet | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| On-board Audio | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | No | Linux driver crashes. | ||||||

| On-board Modem | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board FireWire | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board Smartcard reader | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board CompactFlash | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board PCMCIA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board Wifi | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board Bluetooth | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board SD card reader | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Add-on slots/cards | ||||||||

| ISA add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Audio/Modem-Riser (AMR/CNR) cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | I've an ath9k wifi PCI card and it works. | ||||||

| Mini-PCI add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Mini-PCI-Express add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| PCI-X add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| AGP graphics cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x1 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| PCI Express x2 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x4 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x8 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x16 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | WIP | a clean way to merge the patch must be found. | ||||||

| PCI Express x32 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| HTX add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Legacy / Super I/O | ||||||||

| Floppy | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | There is no floppy connector at all. | ||||||

| Serial port 1 (COM1) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | COM1 is only pin header on board. DB-9 serial connector is available, but not included with board. | ||||||

| Serial port 2 (COM2) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Parallel port | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | No connector, pins on board only | ||||||

| PS/2 keyboard | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| PS/2 mouse | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Game port | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Infrared | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PC speaker | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| DiskOnChip | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Input | ||||||||

| Trackpoint | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Touchpad | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Fn Hotkeys | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Fingerprint Reader | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Laptop | ||||||||

| Docking VGA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking LAN | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking USB | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking Audio | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking Displayport | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Thinklight | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Webcam | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Miscellaneous | ||||||||

| Sensors / fan control | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Hardware watchdog | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| SMBus | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| CAN bus | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| CPU frequency scaling | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | works in GNU/Linux | ||||||

| Other powersaving features | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| ACPI | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Reboot | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| Poweroff | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| Suspend | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| Nonstandard LEDs | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | | |||||||

| High precision event timers (HPET) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | | |||||||

| Random number generator (RNG) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Wake on modem ring | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Wake on LAN | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | | |||||||

| Wake on keyboard | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Wake on mouse | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| TPM | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| Flashrom | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | The chip is SPI | ||||||

Introduction

This pages is about the port to the M4A785T-M, this mainboard is very similar to the M4A785-M, but:

- it has DDR3 instead of DDR2

Building the serial port adapter

You'll need to build a serial port adapter to get the coreboot logs during.

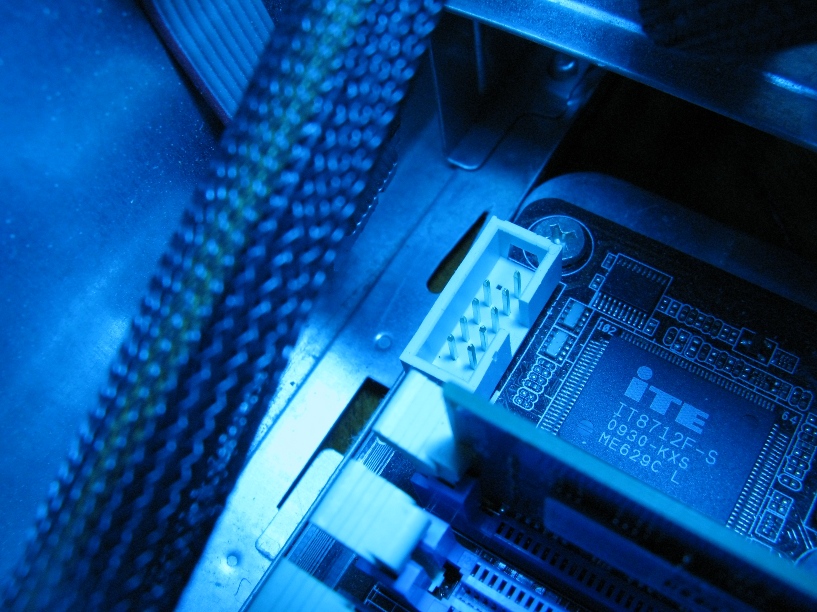

Here's a picture of the serial port connector on the mainboard:

And here's the kind of cable you will need:

And you'll need to build a cable similar to this one(on the picture the DB9 is connector is a male connector):

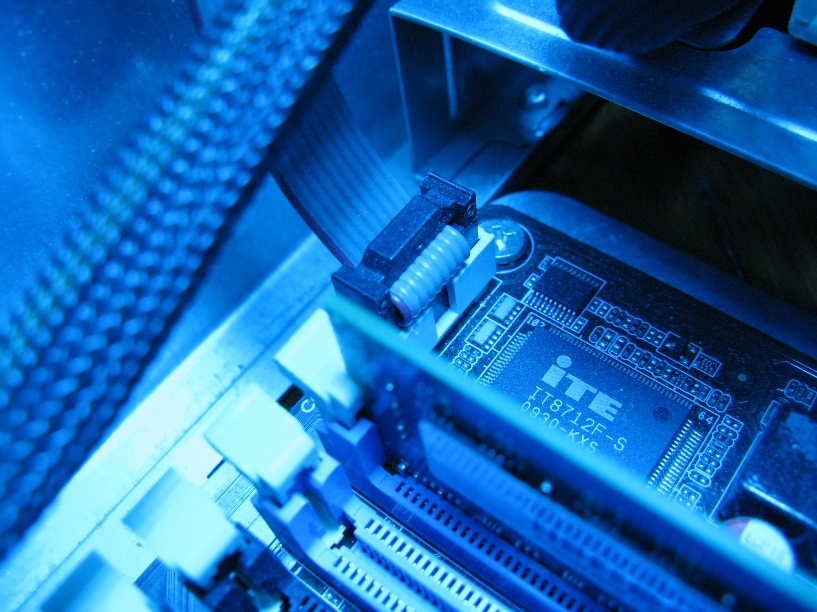

Here's how it looks like on the mainboard:

_____________________ | |NC|09| |08|07| |06|05| |04|03| |02|01| | |

Here's a table of corresponding pins:

| Mainboard connector pin | Mainboard pin Function | Standard DE9 pin connector | Standard DE9 pin Function | Mandatory for coreboot |

|---|---|---|---|---|

| 1 | ? | ? | ? | No |

| 2 | RX | 3 | TX | Yes (you could do without but it's advised to get it, to be able to use certain functions of coreboot) |

| 3 | TX | 2 | RX | Yes |

| 4 | 4 | DTR | No | |

| 5 | Ground | 5 | Ground | Yes |

| 6 | ? | ? | ? | No |

| 7 | 7 | RTS | No | |

| 8 | 8 | CTS | No | |

| 9 | ? | ? | ? | No |

Adapting GNU/Linux

Before booting with coreboot, do the following:

- blacklist the snd-hda* modules (refer to the usual way to get help for the GNU/Linux distribution you want to run for doing that)

- 32bit GNU/Linux trisquel distribution tested

- 64bit GNU/Linux trisquel distribution failed to initialize the USB.

Building Coreboot

To build coreboot for this mainboard:

- checkout coreboot revision 1b1309f289d6fc9f6ec348686665d25218535030

- Configure and Build it as usual(for having graphics you need to extract your VGA BIOS ROM from your BIOS)

PCIe

Patch 1

Patch1 Requirements/Issues

- the -pae kernel didn't boot my LUKS hdd(failed at cryptsetup password entering)... => using a -generic kernel worked(however that sees only 2772M in htop(I've 4GB))

- if you remove the PCIe card, the integrated ATI card won't come up...

- you only see the external graphic card in lspci, like with the BIOS, which seem to be the way to go...

Patch1

From ab15ce791543cb0c1a09317962fe6bdc79e4e1b3 Mon Sep 17 00:00:00 2001 From: Denis 'GNUtoo' Carikli <GNUtoo@no-log.org> Date: Tue, 18 Sep 2012 19:35:44 +0200 Subject: [PATCH] IRQ tables for getting the PCIe graphic card working Thanks a lot for the help trough IRC in the #coreboot channel on the Freenode servers. Change-Id: Ie99ee5adaf997cb94c96eb1942d1089ab2528f85 Signed-off-by: Denis 'GNUtoo' Carikli <GNUtoo@no-log.org> --- src/mainboard/asus/m4a785t-m/devicetree.cb | 6 +++--- 1 files changed, 3 insertions(+), 3 deletions(-) diff --git a/src/mainboard/asus/m4a785t-m/devicetree.cb b/src/mainboard/asus/m4a785t-m/devicetree.cb index e8764b1..7095afd 100644 --- a/src/mainboard/asus/m4a785t-m/devicetree.cb +++ b/src/mainboard/asus/m4a785t-m/devicetree.cb @@ -10,8 +10,8 @@ chip northbridge/amd/amdfam10/root_complex device pci 18.0 on # northbridge chip southbridge/amd/rs780 device pci 0.0 on end # HT 0x9600 - device pci 1.0 on end # Internal Graphics P2P bridge 0x9602 - device pci 2.0 off end # PCIE P2P bridge (external graphics) 0x9603 + device pci 1.0 off end # Internal Graphics P2P bridge 0x9602 + device pci 2.0 on end # PCIE P2P bridge (external graphics) 0x9603 device pci 3.0 off end # PCIE P2P bridge 0x960b device pci 4.0 off end # PCIE P2P bridge 0x9604 device pci 5.0 off end # PCIE P2P bridge 0x9605 @@ -24,7 +24,7 @@ chip northbridge/amd/amdfam10/root_complex register "gpp_configuration" = "3" # Configuration D default register "port_enable" = "0x6fc" register "gfx_dev2_dev3" = "1" - register "gfx_dual_slot" = "2" + register "gfx_dual_slot" = "0" register "gfx_lane_reversal" = "0" register "gfx_tmds" = "0" -- 1.7.5.4

Patch 2

Patch2 Requirements/Issues

- see both cards and memory regions have some issues because of that.

- VESA works

- -pae works

- nouveau fails like that:

[drm] nouveau 0000:02:00.0: Detected an NV50 generation card (0x0a8280b1) [drm] nouveau 0000:02:00.0: Failed to PRAMIN BAR nouveau 0000:02:00.0: PCI INT A disabled nouveau: probe of 0000:02:00.0 failed with error -12

Which is caused by:

pci 0000:02:00.0: BAR 1: trying firmware assignment [mem 0xa0000000-0xafffffff 64bit pref] pci 0000:02:00.0: BAR 1: [mem 0xa0000000-0xafffffff 64bit pref] conflicts with reserved [mem 0xaffe0000-0xbfffffff] pci 0000:02:00.0: BAR 1: can't assign mem pref (size 0x10000000) pci 0000:02:00.0: BAR 3: trying firmware assignment [mem 0xb0000000-0xb1ffffff 64bit pref] pci 0000:02:00.0: BAR 3: [mem 0xb0000000-0xb1ffffff 64bit pref] conflicts with reserved [mem 0xaffe0000-0xbfffffff] pci 0000:02:00.0: BAR 3: can't assign mem pref (size 0x2000000)

Patch2

diff --git a/src/mainboard/asus/m4a785t-m/devicetree.cb b/src/mainboard/asus/m4a785t-m/devicetree.cb

index e8764b1..905e5d3 100644

--- a/src/mainboard/asus/m4a785t-m/devicetree.cb

+++ b/src/mainboard/asus/m4a785t-m/devicetree.cb

@@ -11,7 +11,7 @@ chip northbridge/amd/amdfam10/root_complex

chip southbridge/amd/rs780

device pci 0.0 on end # HT 0x9600

device pci 1.0 on end # Internal Graphics P2P bridge 0x9602

- device pci 2.0 off end # PCIE P2P bridge (external graphics) 0x9603

+ device pci 2.0 on end # PCIE P2P bridge (external graphics) 0x9603

device pci 3.0 off end # PCIE P2P bridge 0x960b

device pci 4.0 off end # PCIE P2P bridge 0x9604

device pci 5.0 off end # PCIE P2P bridge 0x9605

@@ -24,7 +24,7 @@ chip northbridge/amd/amdfam10/root_complex

register "gpp_configuration" = "3" # Configuration D default

register "port_enable" = "0x6fc"

register "gfx_dev2_dev3" = "1"

- register "gfx_dual_slot" = "2"

+ register "gfx_dual_slot" = "0"

register "gfx_lane_reversal" = "0"

register "gfx_tmds" = "0"

SerialICE

- Selecting the ASUS M4A77TD-PRO mainboard makes the serialICE shell appear once flashed(however running the BIOS under SerialICE fails at some point).

Howto

git clone http://review.coreboot.org/p/serialice.git cd serialice make menuconfig make

Failing

It fails like that:

[f000:8943] 3e52.3e54 NVram: [0e] => 00 [f000:8941] 3e52.3e57 NVram: [4d] => 01 [f000:bbe5] 3e64.3e65 IO,PCI: outl 0cf8 <= 8000a040 [f000:bc01] 3e64.3e66 PCI: 0:14.0 [41] => 13 [f000:bc01] 3e64.3e66 IO,PCI: inb 0cfd => 13 [f000:bc2f] 3e67.3e68 IO,PCI: outl 0cf8 <= 8000a040 [f000:bc4d] 3e67.3e69 PCI: 0:14.0 [41] <= 13 [f000:bc4d] 3e67.3e69 IO,PCI: outb 0cfd <= 13 [f000:bdc2] 3e6a.3e6b IO,PCI: outl 0cf8 <= 8000a348 [f000:bc03] 3e6a.3e6c PCI: 0:14.3 [48] => 13 [f000:bc03] 3e6a.3e6c IO,PCI: inb 0cfc => 13 [f000:bda0] 3e6d.3e6e IO,PCI: outl 0cf8 <= 8000a348 [f000:bc4b] 3e6d.3e6f PCI: 0:14.3 [48] <= 13 [f000:bc4b] 3e6d.3e6f IO,PCI: outb 0cfc <= 13 [f000:bbe5] 3e70.3e71 IO,PCI: outl 0cf8 <= 8000a36c [f000:bc01] 3e70.3e72 PCI: 0:14.3 [6c] => b0 [f000:bc01] 3e70.3e72 IO,PCI: inb 0cfc => b0 [f000:bc2f] 3e73.3e74 IO,PCI: outl 0cf8 <= 8000a36c [f000:bc4d] 3e73.3e75 PCI: 0:14.3 [6c] <= b0 [f000:bc4d] 3e73.3e75 IO,PCI: outb 0cfc <= b0 [f000:3d80] 3e7e.3e7f CPU MSR: [00000201] => 00000000.00000000 [f000:3d89] 3e7e.3e80 CPU MSR: [00000201] <= 00000000.00000000 [f000:3d80] 3e7e.3e81 CPU MSR: [00000203] => 00000000.00000000 [f000:3d89] 3e7e.3e82 CPU MSR: [00000203] <= 00000000.00000000 [f000:3d80] 3e7e.3e83 CPU MSR: [00000205] => 00000000.00000000 [f000:3d89] 3e7e.3e84 CPU MSR: [00000205] <= 00000000.00000000 [f000:3d80] 3e7e.3e85 CPU MSR: [00000207] => 00000000.00000000 [f000:3d89] 3e7e.3e86 CPU MSR: [00000207] <= 00000000.00000000 [f000:3d80] 3e7e.3e87 CPU MSR: [00000209] => 00000000.00000000 [f000:3d89] 3e7e.3e88 CPU MSR: [00000209] <= 00000000.00000000 [f000:3d80] 3e7e.3e89 CPU MSR: [0000020b] => 00000000.00000000 [f000:3d89] 3e7e.3e8a CPU MSR: [0000020b] <= 00000000.00000000 [f000:3d80] 3e7e.3e8b CPU MSR: [0000020d] => 00000000.00000000 [f000:3d89] 3e7e.3e8c CPU MSR: [0000020d] <= 00000000.00000000 [f000:3d80] 3e7e.3e8d CPU MSR: [0000020f] => 00000000.00000000 [f000:3d89] 3e7e.3e8e CPU MSR: [0000020f] <= 00000000.00000000 [f000:3deb] 3e7e.3eb0 CPU MSR: [0000020f] => 00000000.00000000 [f000:3def] 3e7e.3eb1 CPU MSR: [0000020f] <= 00000000.00000000 [f000:3deb] 3e7e.3eb2 CPU MSR: [0000020d] => 00000000.00000000 [f000:3def] 3e7e.3eb3 CPU MSR: [0000020d] <= 00000000.00000000 [f000:3deb] 3e7e.3eb4 CPU MSR: [0000020b] => 00000000.00000000 [f000:3def] 3e7e.3eb5 CPU MSR: [0000020b] <= 00000000.00000000 [f000:3deb] 3e7e.3eb6 CPU MSR: [00000209] => 00000000.00000000 [f000:3def] 3e7e.3eb7 CPU MSR: [00000209] <= 00000000.00000000 [f000:3deb] 3e7e.3eb8 CPU MSR: [00000207] => 00000000.00000000 [f000:3def] 3e7e.3eb9 CPU MSR: [00000207] <= 00000000.00000000 [f000:3deb] 3e7e.3eba CPU MSR: [00000205] => 00000000.00000000 [f000:3def] 3e7e.3ebb CPU MSR: [00000205] <= 00000000.00000000 [f000:3deb] 3e7e.3ebc CPU MSR: [00000203] => 00000000.00000000 [f000:3def] 3e7e.3ebd CPU MSR: [00000203] <= 00000000.00000000 [f000:3deb] 3e7e.3ebe CPU MSR: [00000201] => 00000000.00000000 [f000:3def] 3e7e.3ebf CPU MSR: [00000201] <= 00000000.00000000 [f000:22d7] 3eda.3edb CPUID: eax: 00000001; ecx: 00004000 => 00100f62.00020800.00802009.178bfbff [f000:8943] 3edc.3ede NVram: [4d] => 01 [f000:2207] 3ef4.3ef5 CPU MSR: [c0010020] <= 00000000.fffad3a0

With:

$ cat asus_m4a77td_pro.lua

dofile("i82801.lua")

function do_mainboard_setup()

do_default_setup()

enable_hook_i82801dx()

-- Apply mainboard hooks last, so they are the first ones to check

--enable_hook(io_hooks, filter_mainboard)

end

TODO

- Add defaults for the nvram settings.

- find a clean way to merge the patch for the PCIe graphic card.

- fix the Audio CODEC(it's the same than the x60 and it works on the x60):

<DarkDefender> GNUtoo-hplaptop: I think you should be able to disable it if you look at "src/southbridge/amd/cimx/sb700/late.c" and line 266

- handle suspend to ram

- lock SMM/SMI

- make it possible to run the BIOS under serialICE

- 64bit support